Ali Saadoon Ahmed

**Al-Maaref University College**

**Microprocessors**

Ex : Write an ALP to evaluate x(y + z) where x = 10H, y = 20H and z = 30H and store the result in a memory location 54000H.

MOV AX ,  $5000\mathrm{H}$

MOV DS , AX  $% \left( AX\right) =\left( AX\right) \left( AX$

MOV AL , 20H

MOV CL, 30H

ADD AL, CL

MOV CL, 10H

MUL CL

MOV SI , 4000H

MOV [SI] , AX

Ex: Write an ALP to multiply the word 1234H by the double word 12345678H. Store the result in locations starting in 54000H.

| MOV AX , 1234H  | MOV BX , 5678H |

|-----------------|----------------|

| MOV CX , 1234H  | MUL BX         |

| MOV SI , AX     | MOV DI , DX    |

| MOV AX , 1234H  | MUL CX         |

| ADC AX , DI     | ADC DX , 0000H |

| MOV BX , 5000H  | MOV DS, BX     |

| MOV [4000H], SI | MOV [4002H],AX |

| MOV [4004H],DX  | HLT            |

**Note:** After executing **AND**, **OR**, or **XOR** instructions CF and OF are both 0. PF, SF, and ZF are updated . AF is undefined.

Ex : Write an ALP to clear bits 0 to 5, set bits 6 to 10 and complement bits 11 to 15 in a memory location 34000H.

Ans.

MOV AX ,  $3000\mathrm{H}$

MOV DS , AX

AND [4000], FFC0H

OR [4000], 07C0H

XOR [4000], F800H

#### HLT

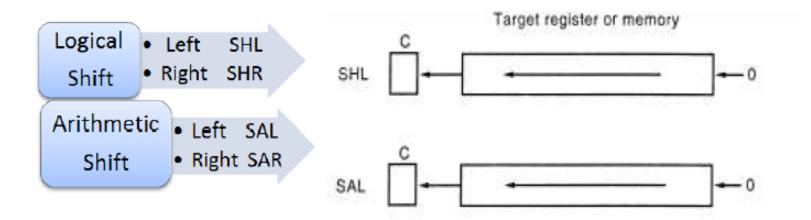

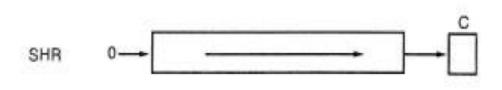

#### **Shift Instructions:**

Shift instructions can perform two basic types of shift operations: **the logical shift** and **the arithmetic shift**. Also, each of these operations can be performed to the right or to the left. They have the ability to shift the contents of either an internal register or a storage location in memory.

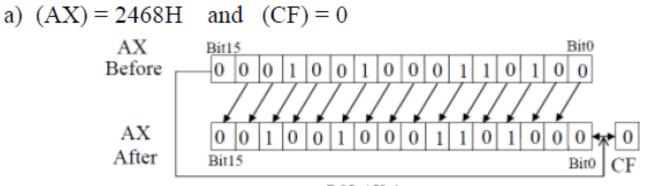

#### Ex: If (AX)=1234H, then, executing: SHL AX, 1

(AX) = 2468H & (CF)=0

Ex: If (CL)=2 and (AX)= 1234AH. Then, executing: SAR AX, CL leads to: (AX)=048EH & (CF)=0

| Mnemonic | Meaning                                             | Format                                     | Operation                                                                                  | Flags<br>affected                                            |

|----------|-----------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| SAL/SHL  | Shift<br>arithmetic left /<br>Shift logical<br>left | SHL D,1<br>SHL D,CL<br>SAL D,1<br>SAL D,CL | Shift D (Reg. / Mem.)<br>to left either by 1 bit or<br>by number of bits<br>stored in CL . | CF, PF, SF, Z<br>AF undefined<br>OF undefined<br>if count ≠1 |

| SHR      | Shift logical<br>right                              | SHR D,1<br>SHR D,CL                        | Shift D (Reg. / Mem.)<br>to right either by 1 bit<br>or by number of bits<br>stored in CL. | CF, PF, SF, Z<br>AF undefined<br>OF undefined<br>if count ≠1 |

| SAR      | Shift<br>arithmetic<br>right                        | SAR D,1<br>SAR D,CL                        | Shift D (Reg. / Mem.)<br>either by 1 bit or by<br>number of bits stored<br>in CL.          | CF, PF, SF, Z<br>AF undefined<br>OF undefined<br>if count ≠1 |

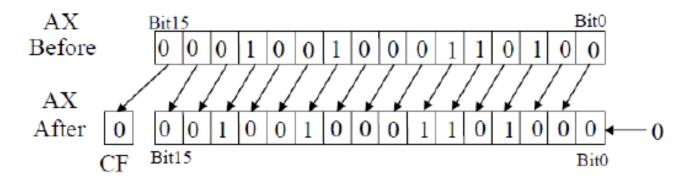

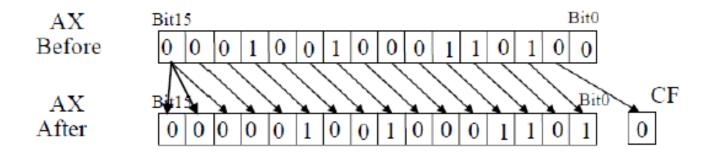

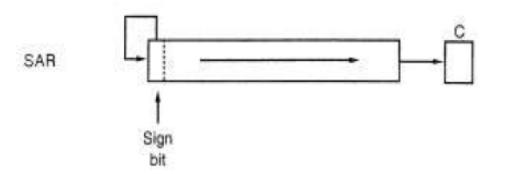

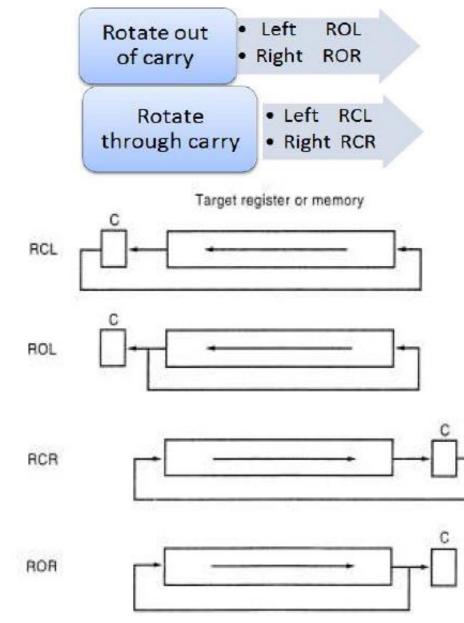

#### Rotate (ROL, ROR, RCL, and, RCR ) Instructions:

Rotate instructions, are similar to the shift instructions. The operation of these instructions is described below. They have the ability to rotate the contents of either an internal register or a storage location in memory.

| Mnemonic | Meaning                          | Format              | Operation                                                                                   | Flags<br>affected                 |

|----------|----------------------------------|---------------------|---------------------------------------------------------------------------------------------|-----------------------------------|

| ROL      | Rotate left                      | ROL D,1<br>ROL D,CL | Rotate D (Reg./Mem.) left<br>out of carry either by 1 bit<br>or No. of bits stored in CL .  | CF<br>OF undefined<br>if count ≠1 |

| ROR      | Rotate right                     | ROR D,1<br>ROR D,CL | Rotate D (Reg./Mem.) right<br>out of carry either by 1 bit<br>or No. of bits stored in CL . | CF<br>OF undefined<br>if count ≠1 |

| RCL      | Rotate left<br>through<br>carry  | RCL D,1<br>RCL D,CL | Rotate D (Reg./Mem.) left<br>through carry either by 1<br>bit or No. of bits in CL .        | CF<br>OF undefined<br>if count ≠1 |

| RCR      | Rotate right<br>through<br>carry | RCR D,1<br>RCR D,CL | The same operation of RCL but to the right.                                                 | CF<br>OF undefined<br>if count ≠1 |

#### Rotate (ROL, ROR, RCL, and, RCR ) Instructions:

Rotate instructions, are similar to the shift instructions. The operation of these instructions is described below. They have the ability to rotate the contents of either an internal register or a storage location in memory.

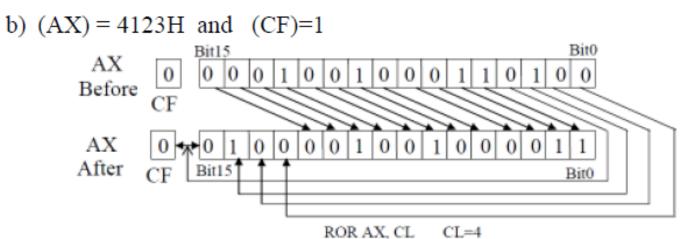

**Ex** : If (CL) =04<sub>16</sub> and AX=1234A<sub>16</sub>. Determine the new contents of AX and the carry flag after executing the instructions: a) ROL AX, 1 b) ROR AX, CL

#### Ans.

#### **Flags Control Instructions**

The flag control instruction affect the state of the flags directly, these instructions and their operation are listed below:

| Mnemonic | Meaning             | Operation    | Flags affected |

|----------|---------------------|--------------|----------------|

| LAHF     | Load AH from flags  | (AH)←(Flags) | None           |

| SAHF     | Store AH into flags | (Flags)←(AH) | SF,ZF,AF,PF,CF |

LAHF instruction : Load (copy to) AH with the low byte the flag register.

$(AH) \leftarrow (Low byte of flag register)$

SAHF instruction Store (copy) AH register to low byte of flag register.

(Low byte of flag register)  $\leftarrow$  (AH)

## Ex: Write an ALP that complements the first byte of flags register.

LAHF

XOR AH , 0FFH

SAHF

HLT

| Mner | monic | Meaning |                  | Operation          |        | Flags affected |    |                   |

|------|-------|---------|------------------|--------------------|--------|----------------|----|-------------------|

| С    | LC    | Clea    | Clear carry flag |                    | (CF)←0 |                | CF |                   |

| S    | тс    | Set     | Set carry flag   |                    | (CF)←1 |                | CF |                   |

| C    | мс    | Com     | plement carry fl | flag (CF)←NOT (CF) |        | CF             |    |                   |

| С    | :LI   | Clea    | r interrupt flag | (IF)←0             |        | IF             |    |                   |

| S    | TI    | Set     | interrupt flag   | (IF)←1             |        | -1             | IF |                   |

|      | Mnem  | onic    | Meaning          | For                | mat    | Operation      | ı  | Flags<br>affected |

|      | CL    | D       | Clear DF         | CLD                |        | (DF)←0         |    | DF                |

|      | ST    | D       | Set DF           | STD                |        | (DF)←1         |    | DF                |

#### **Compare CMP and TEST Instructions**

The following are the characteristics of CMP instruction:

- Can compare two 8-bit or two 16-bit numbers.

- Operands many reside in memory, a register in the CPU or be a part of an instruction.

- CMP is a subtraction method, it uses 2's complement.

- Result of CMP is not saved in the destination operand.

- Results of comparison is reflected in the six status flags: CF, AF, OF, PF, SF and ZF.

| Mnemonic | Meaning | Format   | Operation                                            | Flags affected            |

|----------|---------|----------|------------------------------------------------------|---------------------------|

| СМР      | Compare | CMP D, S | (D)-(S) is used in setting<br>or resetting the flags | CF, AF, OF, PF, SF,<br>ZF |

| Destination | Source    |

|-------------|-----------|

| Register    | Register  |

| Register    | Memory    |

| Memory      | Register  |

| Register    | Immediate |

| Memory      | Immediate |

| Accumulator | Immediate |

#### Examples

CMP AX , BX CMP DL , CL CMP AL , [BX] CMP CX , 1234h CMP [SI+100H] , 1234H

CMP AX , BX

$AX > BX \rightarrow CF = 0$   $AX < BX \rightarrow CF = 1$  $AX = BX \rightarrow ZF = 1$

#### **The TEST Instruction**

This instruction ANDs the contents of a source byte or word with the contents of specified destination word. Flags are updated but neither operand is changed. TEST instruction is often used to set flags before a conditional jump instruction.

| Mnemonic | Meaning | Format    | Operation | Flags Affected |

|----------|---------|-----------|-----------|----------------|

| TEST     | test    | TEST D, S | (D) . (S) | PF,ZF,SF       |

#### **Computer Science Dept.**